Aufgabenstellung

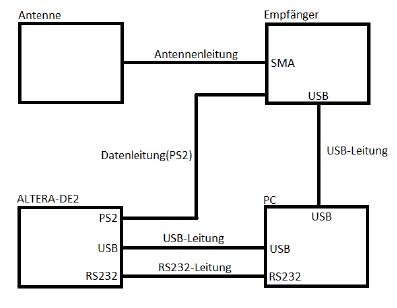

Aufgabenstellung in dieser Bachelor-Thesis war es den Aufbau des Projektes Implementierung eines Mode-S/ADS-B Decoders in VHDL in ein eigenstûÊndiges und leicht zu bedienendes GerûÊt zu û¥berfû¥hren. Dazu sollten alle Komponenten auf einem Board zusammengefû¥hrt und optimiert werden. Damit das Board ohne groûen Aufwand in Betrieb genommen werden kann, musste sichergestellt werden, dass das Board selbststûÊndig nach dem Anschlieûen den Betrieb aufnimmt. Um die Leistung weiter zu erhûÑhen, sollte die Anzahl der EmpfûÊnger erhûÑht werden. Ziel war daher das Design und die Inbetriebnahme eines FPGA-basierten Boards, das speziell auf den Empfang von ADS-B ausgerichtet ist.